#### Imperial College London

MSc in Analogue & Digital IC Design

# Clocked circuits, Shift Registers & BCD converter

Peter Cheung

Department of Electrical & Electronic Engineering

Imperial College London

Course webpage: www.ee.ic.ac.uk/pcheung/teaching/MSc\_Experiment/ E-mail: p.cheung@imperial.ac.uk

PYKC 19 Oct 2017

MSc Lab - Mastering Digital Design

Lecture 2 Slide 1

I hope you have completed Part 1 of the Experiment. This lecture leads you to Part 2 of the experiment and hopefully helps you with your progress to Part 2. It covers a number of topics:

- 1. How do we specify clocked (i.e. sequential) circuits in Verilog?

- 2. How do we specify a flexible counter?

- 3. How to specify and use shift registers?

- 4. How to specify linear-feedback shift registers as a pseudo random binary sequence generator?

- 5. How to convert binary (or hexadecimal) numbers to binary coded decimal (BCD) numbers?

## **Power of Verilog: Integer Arithmetic**

Arithmetic operations make computation easy:

```

module add32(a, b, sum);

input[31:0] a,b;

output[31:0] sum;

assign sum = a + b;

endmodule

```

Here is a 32-bit adder with carry-in and carry-out:

```

module add32_carry(a, b, cin, sum, cout);

input[31:0] a,b;

input cin;

output[31:0] sum;

output cout;

assign {cout, sum} = a + b + cin;

endmodule

```

PYKC 19 Oct 2017

MSc Lab - Mastering Digital Design

Lecture 2 Slide 2

Verilog is very much like C. However, the declaration of **a**, **b** and **sum** in the **module add32** specifies the data width (i.e. number of bits in each signal **a**, **b** or **sum**). This is often known as a "**vector**" or a "**bus**". Here the data width is 32-bit, and it is ranging from bit 31 down to bit 0 (e.g. **sum[31:0]**).

You can refer to individual bits using the index value. For example, the least-significant bit (LSB) of sum is **sum[0]** and the most-significant bit (MSB) is **sum[31]**. **sum[7:0]** refers the the least-significant byte of **sum**.

The '+' operator can be used for signals of any width. Here a 32-bit add operation is specified. **sum** is also 32-bit in width. However, if **a** and **b** are 32-bit wide, the sum result could be 33-bit (including the carry out). Therefore this operation could result in a wrong answer due to **overflow** into the carry bit. The 33th bit is truncated. The second example **module add32\_carry** shows the same adder but with carry input and carry output. Note the LHS of the **assign** statement. The **{cout, sum}** is a **concatenation** operator – the contents inside the brackets **{}** are concatenated together, with **cout** is assigned the MSB of the 33th bit of the result , and the remaining bits are formed by **sum[31:0]**.

- Bitwise operators: perform bit-sliced operations on vectors bit by bit

- $\Box$  ~(4'b0101) = {~0,~1,~0,~1} = 4'b1010

- □ 4'b0101 & 4'b0011 = 4'b0001

- ◆ Logical operators: return true or false (1-bit) results

- $\Box$  !(4'b0101) = ~1 = 1'b0

- ◆ Reduction operators: act on each bit of a SINGLE input vector

- $\square$  &(4'b0101) = 0 & 1 & 0 & 1 = 1'b0

#### Bitwise

| ~a     | NOT  |  |  |

|--------|------|--|--|

| a & b  | AND  |  |  |

| a b    | OR   |  |  |

| a^b    | XOR  |  |  |

| a ~^ b | XNOR |  |  |

# Logical

|   | !a     | NOT |  |  |

|---|--------|-----|--|--|

|   | a && b | AND |  |  |

| I | a    b | OR  |  |  |

|   |        |     |  |  |

Note distinction between ~a and !a

Reduction

| &a | AND  |  |  |

|----|------|--|--|

| ~& | NAND |  |  |

|    | OR   |  |  |

| ~  | NOR  |  |  |

| ۸  | XOR  |  |  |

PYKC 19 Oct 2017

MSc Lab - Mastering Digital Design

Lecture 2 Slide 3

3

There are three different types of Boolean operators:

**Bitwise operators** perform what you would expect as if there are parallel gates used for each bit of the operands. Therefore **a&b** means that each bit from **a** and **b** is passed through an AND-gate.

**Logical operators** only result in 0 or 1 (i.e. 1-bit result) In this example !a **(not a)** where **a = 0101**, will result in first, **a** being evaluated as a logical value (i.e. logical '1' or true). Therefore the result **~a** is logical 0 (or false).

**Reduction operators** is applied to a single operand (and sometimes known as unary operators). It performs the operation one-bit at a time to the operand.

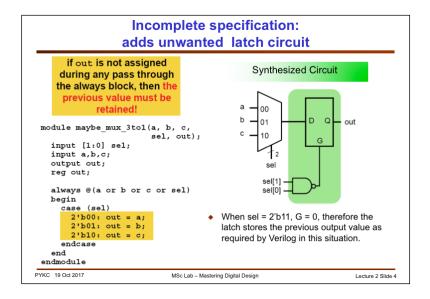

The consequence of this is an unexpected extra latch being added to the hardware. In order to cope with the unspecified condition of **sel = 2'b11**, the output of the MUX is fed to be **latch**.

Noted that a latch is **level-triggered**; a flipflop is **edge-triggered**. A latch has the property that when the gate input **G** is high, **Q** = **D** (i.e. it is **transparent**: input goes straight to output). If **G** is low, the latch become **opaque**, meaning that it retains the previous value

The green shaded latch in the diagram and the controlling NAND gate are the unintended consequences of this incompletely specified 3-to-1 multiplexer.

# Always avoid incomplete specification

· Solution 2: Fully specify all branches of

statement in case construct:

if-else construct, or include a default

Lecture 2 Slide 5

5

Solution 1: Precede all conditionals with a default assignment for all signals:

PYKC 19 Oct 2017

```

always @(a or b or c or sel)

always @(a or b or c or sel)

begin

begin

out = 1'bx;

case (sel)

case (sel)

2'b00: out = a;

2'b00: out = a;

2'b01: out = b;

2'b01: out = b;

2'b10: out = c;

2'b10: out = c;

default: out = 1'bx;

endcase

endcase

end

end

endmodule

endmodule

```

There are two solutions to avoid the unintended latch being added.

**Solution 1** is to put outside the **case** statement a "**default**" value for out. Here **1'bx** (i.e. 'x') means **undefined**.

MSc Lab - Mastering Digital Design

**Solution 2** is better: inside the **case** statement block, always add the **default** line. This will catch ALL the unspecified cases and avoid the introduction of the spurious unintended latches.

Lesson: always include a default assignment in any **case** statement to capture unintended incomplete specification.

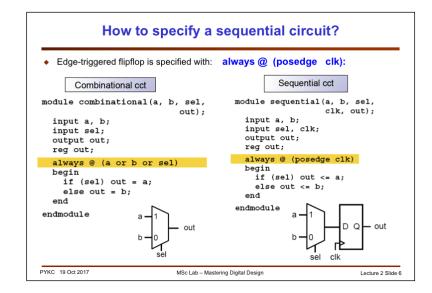

We have previously seen the 2-to-1 MUX being specified as combinational circuit in Verilog using the always construct with the **sensitivity list**.

The right hand diagram shows how a clocked **sequential circuit** is being specified using **always** block, but with a **sensitivity list** that includes the keyword **posedge** (or **negedge**). Note that the clocking signal **clk** is an arbitrary name – you could call it "**fred**" or anything else!

The **sensitivity list** NO LONGER contains the input signals **a**, **b** or **sel**. Instead the hardware is specified to be sensitive the positive edge of **clk**. When this happens, the output changes according to the specification inside the **always** block.

Two assignments ("=" and "<=") are shown here. I will explain the difference between these later.

Therefore in Verilog, you specify flipflops using always **block** in conjunction with the keyword **posedge** or **negedge**.

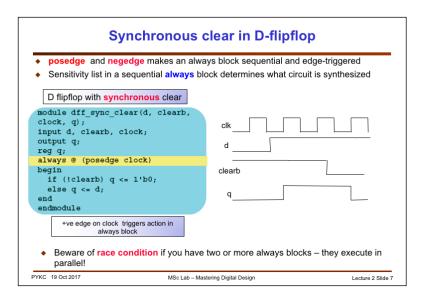

Here is a specification for a D-flipflop with synchronous clear which is low active (i.e. clear the FF when **clearb** is low).

7

You may have more than one always block in a module. But if this is the case, beware that the two always blocks will execute in parallel. Therefore they must NOT specify the same output, otherwise a race condition exists and the result is unpredictable.

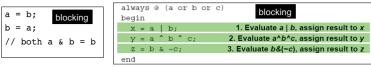

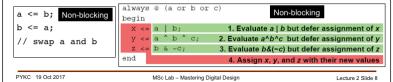

- Verilog has two different types of assignments: blocking & nonblocking.

- Blocking assignments = are executed in the order they appear, therefore they are done

one after another. Therefore the first statement "blocks" the second until it is done,

hence it is called blocking assignments.

Non-blocking assignments <= are executed in parallel. Therefore an earlier statement does not block the later statement. Note the subtle effect this has within always block:

In Verilog '=' is known as **blocking assignment**. They are **executed in the order** they appear within the Verilog simulation environment. So the first '=' assignment blocks the second one. This is very much like what happens in C codes.

In the top left example, both **a** and **b** eventually have the value **b**.

In the top right example, each statement is evaluated in turn and assignment is performed immediately at the end of the statement.

Non-block assignment is '<=', and statements with this assignments are **executed in parallel** (i.e. order do not matter).

In the bottom left example, **a** and **b** are **swapped** over because you can view that the two assignments happen at the same time.

In the bottom right example, three evaluations are made, and the assignment to x, y and z happens at the same time on exiting from the always block.

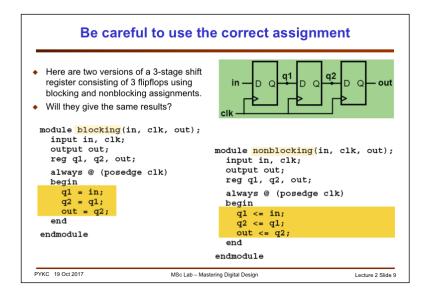

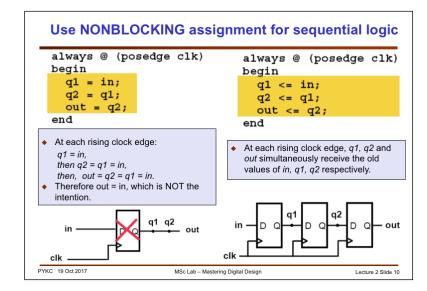

Understanding the difference between '=' and '<=' is important. Suppose we want to specify a three-stage shift register (i.e. three D-FF in series as shown in the schematic).

Here are two possible specification. Which one do you think will create the correct circuit and which one is wrong?

The left hand specification is **wrong**. Since the three assignments are performed in sequence, **out** = **q2** = **q1** = **in**. Therefore the resultant circuit is ONE D-flipflop. The right hand side is **correct**. **q1**, **q2** and **out** are updated simultaneously on exit from the **always** block. Therefore their "original" values MUST be retained. Hence this will result in three D-flipflops being synthesised (i.e. created).

In general, you should always use '<=' inside an always block to specify your circuit.

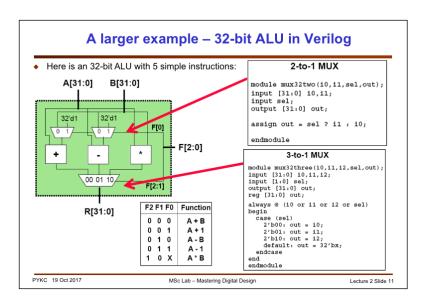

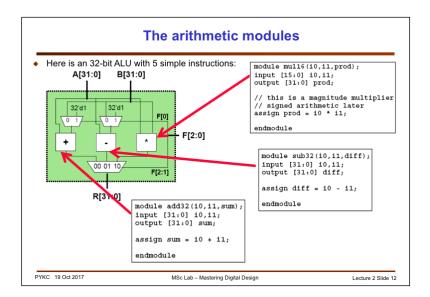

Now let us put all you have learned together in specifying (or designing) a 32-bit ALU in Verilog.

There are five operators in this ALU. We assume that there are three arithmetic blocks, and three multiplexers (two 2-to-1 MUX and one 3-to-1 MUX).

Each hardware block is defined as a Verilog module. So we have the following modules:

mux32two – a 32-bit multiplexer that has TWO inputs

mux32three - a 32-bit multiplexer that has THREE inputs

mul16 – a 16-by-16 binary multiplier that produces a 32-bit product

add32 - a 32-bit binary adder

sub32 – a 32-bit binary subtractor

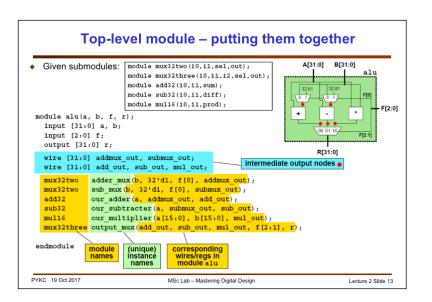

Now let us put all these together.

Note that **mxu32two** is being used twice and therefore this **is instantiated** two times with two different **instance names**: **adder mux** and **sub mux**.

Connections between modules are implicit through the use of signal names. For example, the 16-bit inputs to the multiplier are taken from the lower 16-bits of a and b inputs (i.e. a[15:0] and b[15:0]).

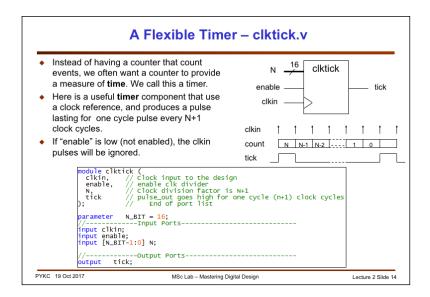

Counters are good in counting events (e.g. clock cycles). We can also use counters to provide some form of time measurement.

Here is a useful component which I can a clock tick circuit. We are not interested in the actual count value. What is needed, however, is that the circuit generates a single clock pulse (i.e. lasting for one clock period) for every N+1 rising edge of the clock input signal **clkin**.

We also add an enable signal, which must be set to  $^\prime 1^\prime$  in order to enable the internal counting circuit.

Shown below is the module interface for this circuit in Verilog.

Note that the **parameter** keyword is used to define the number of bits of the internal counter (or the count value N). This makes the module easily adaptable to different size of counter.

### clktick.v explained • "count" is an internal N BIT counter. 1 1 1 1 1 We use this as a down (instead of up) N N-1 N-2 ---- 1 0 • The counter value goes from N to 0, hence there are N+1 clock cycles for each tick pulse. -----Output Ports Data Type----// Output port can be a storage element (reg) or a wire reg [N\_BIT-1:0] count; reg tick; initial tick = 1'b0; //---- Main Body of the module ----always @ (posedge clkin) if (enable == 1'b1) if (count == 0) tick <= 1'b1; count <= N; else begin tick <= 1'b0; count <= count - 1'b1; endmodule // End of Module clktick PYKC 19 Oct 2017 MSc Lab - Mastering Digital Design Lecture 2 Slide 15

The actual Verilog specification for this module is shown here.

There has to be an internal counter **count** whose output is NOT visible external to this module. This is created with the **reg [N BIT-1:0] count**; statement.

The output **tick** has to be declared as **reg** here because its value is updated inside the always block.

Also note that instead of adding '1' on each positive edge of the clock, this design uses a **down** counter. The counter counts from N to 0 (hence N+1 clock cycles). When that happens, it is reset to N and the tick output is high for the next clock cycle.

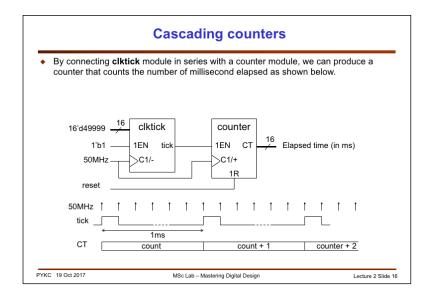

Using this style of designing a clock tick circuit allows us to easily connect multiple counters in series as shown here.

The **clktick** module is producing a pulse on the **tick** output every 50,000 cycles of the 50MHz clock. Therefore **tick** goes high for 20 microsecond once every 1 msec (or 1KHz).

The **clktick** module is sometimes called a **prescaler** circuit. It prescale the input clock signal (50MHz) in order for the second counter to count at a lower frequency (i.e. 1KHz).

The second counter is now counting the number of millisecond that has been elapsed since the last time reset 1R goes high.

The design of this circuit is left as a tutorial problem for you to do.

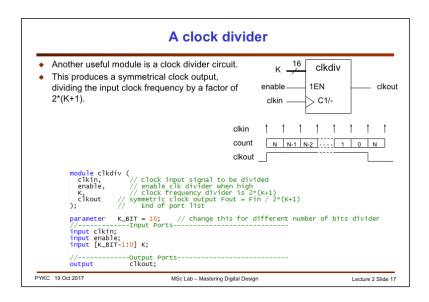

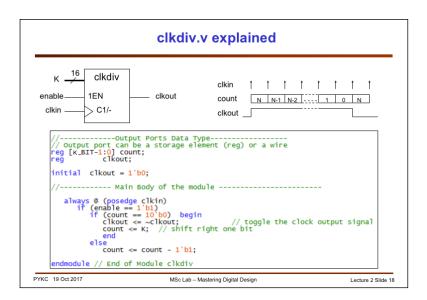

Here is yet another useful form of a counter. I call this a clock divider. Unlike the **clktick** module, which produces a one cycle tick signal every N+1 cycle of the clock, this produces a symmetric clock output **clkout** at a frequency that is 2\*(K+1) lower than the input clock frequency. Shown here is the module interface in Verilog. Again we have used the **parameter** statement to make this design ease of modification for different internal counter size.

The Verilog specification is similar to that for **clktick**. This also has an internal counter that counts from K to 0, then the output **clkout** is toggled whenever the count value reaches 0.

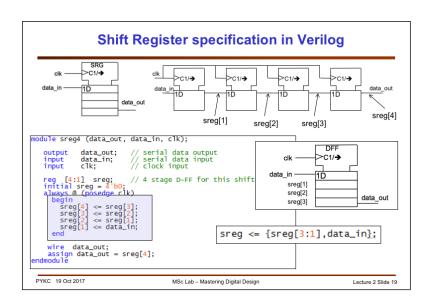

To specify a shift register in Verilog, use the code shown here (in blue box). We use <= assignment to make sure that **sreg[4:1]** are updated only at the end of the always block.

On the right is a short-hand version of the four assignment statements:

```

sreg <= {sreg[3:1], data_in}</pre>

```

This way of specifying the input to the assignment is powerful. We use the concatenation operation { .... } to make up four bits from sreg[3:0] and data\_in (with data\_in being the LSB) and assign it to sreg[4:1].

19

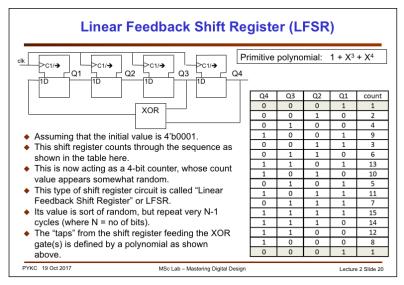

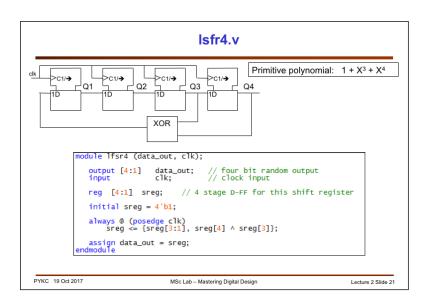

We can also make a shift register count in binary, but in an interesting sequence. Consider the above circuit with an initial state of the shift register set to 4'b0001. The sequence that this circuit goes through is shown in the table here. It is NOT counting binary. Instead it is counting in a sequence that is sort of **random**. This is often called a pseudo random binary sequence (or counter).

The shift register connect this way is also known as a "Linear Feedback Shift Register" or LFSR. There is a whole area of mathematics devoted to this type of computation, known as "finite fields" which we will not consider on this course. The circuit shown below is effective implementing a sequence defined by a polynomial shown:  $1 + X^3 + X^4$ . The term "1" specifies the input to the left-most D-FF. This signal is derived as an XOR function (which is the finite field '+') of two signals "tapped" from stage 3 (i.e.  $X^3$ ) and stage 4 (i.e.  $X^4$ ) of the shift register.

For a m stage LFSR, where m is an integer, one could always find a polynomial (i.e. tap configuration) that will provide maximal length. This means that the sequence will only repeat after 2<sup>m</sup>-1 cycles. Such a polynomial is known as a "primitive polynomial".

| m  |                              | m  |                                 |

|----|------------------------------|----|---------------------------------|

| 3  | $1 + X + X^3$                | 14 | $1 + X + X^6 + X^{10} + X^{14}$ |

| 4  | $1 + X + X^4$                | 15 | $1 + X + X^{15}$                |

| 5  | $1 + X^2 + X^5$              | 16 | $1 + X + X^3 + X^{12} + X^{16}$ |

| 6  | $1 + X + X^6$                | 17 | $1 + X^3 + X^{17}$              |

| 7  | $1 + X^3 + X^7$              | 18 | $1 + X^7 + X^{18}$              |

| 8  | $1 + X^2 + X^3 + X^4 + X^8$  | 19 | $1 + X + X^2 + X^5 + X^{19}$    |

| 9  | $1 + X^4 + X^9$              | 20 | $1 + X^3 + X^{20}$              |

| 10 | $1 + X^3 + X^{10}$           | 21 | $1 + X^2 + X^{21}$              |

| 11 | $1 + X^2 + X^{11}$           | 22 | $1 + X + X^{22}$                |

| 12 | $1 + X + X^4 + X^6 + X^{12}$ | 23 | $1 + X^5 + X^{23}$              |

| 13 | $1 + X + X^3 + X^4 + X^{13}$ | 24 | $1 + X + X^2 + X^7 + X^{24}$    |

The table here shows some of the popular primitive polynomials for different value of m.

Since the output of such a counter is peudorandom, it is a commonly used circuit to produce random binary sequence for different applications.

Here is the Verilog specification for a 4-bit LFSR.

- As the part 1 of the Lab Experiment VERI, you will be implementing the 7 segment decoder we designed in the last lecture. This will show every four binary bits as a hexadecimal digit on the display.

- Hex numbers are difficult to interpret. Often we would like to see the binary value displayed as decimal. For that we need to design a combinational circuit to converter from binary to binary-coded decimal. For example, the value 8'hff or 8'b111111111 is converted to 8'd255 in decimal.

PYKC 19 Oct 2017 MSc Lab – Mastering Digital Design Lecture 2 Slide 22

We now take another example of a relative complex combinational circuit, and see how we can specify our design in Verilog.

The goal is to design a circuit that converts an 8-bit binary number into three x 4-bit binary coded decimal values (i.e. 12 bit).

There is a well-known algorithm called "shift-and-add-3" algorithm to do this conversion. For example, if we take 8-bit hexadecimal number 8'hff (i.e. all 1's), it has two hex digits. Once converted to binary coded decimal (BCD) it becomes 255 (3 BCD digits).

#### Shift and Add 3 algorithm [1] - shifting operation ◆ Let us consider converting hexadecimal number 8'h7c (which is decimal 8'd124) ◆ Shift the 8-bit binary number left by 1 bit = multiply number by 2 Shifting the number left 8 times = multiply number by 2<sup>8</sup> Now truncate the number by dropping the bottom 8 bits = divide number by 2<sup>8</sup> ◆ So far we have done nothing to the number – it has the same value • The idea is that, as we shift the number left into the BCD digit "bins", we make the necessary conversion to the hex number so that it confirms to the BCD rule (i.e. falls within 0 to 9. instead of 0 to 15) 8-bit binary 0 1 1 1 1100 Original binary number Shift left 8 times 0 1 1 1 1 1 0 0 0 0 0 0 0000 (same as multiply by 28) Truncate the lower 8 bits 0 1 1 1 1 1 0 0 (same as divide by 28) PYKC 19 Oct 2017 MSc Lab - Mastering Digital Design Lecture 2 Slide 23

Before we examine this algorithm in detail, let us consider the arithmetic operation of shifting left by one bit. This is the same as a  $\times$  2 operation.

If we do it 8 times, then we have multiplied the original number by 256 or 28.

Now if you ignore the bottom 8-bit through a truncation process, you effectively divide the number by 256. In other words, we get back to the original number in binary (or in hexadecimal).

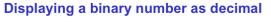

## Shift and Add 3 algorithm [2] – shift left with problem

- If we take the original 8-bit binary number and shift this three times into the BCD digit positions. After 3 shifts we are still OK, because the **ones digit** has a value of 3 (which is OK as a BCD digit).

- If we shift again (4<sup>th</sup> time), the digit now has a value of 7. This is still OK. However, no matter what the next bit it, another shift will make this digit illegal (either as hexadecimal "e" or "f", both not BCD).

- In our case, this will be a "f"!

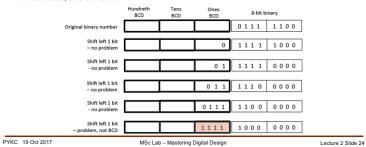

Our conversion algorithms works by shift the number left 8 times, but each time make an adjustment (or correction) if it is NOT a valid BCD digit.

Let us consider this example. We can shift the number four time left, and it will give a valid BCD digit of 7.

However, if we shift left again, then 7 becomes hex F, which is NOT valid. Therefore the algorithm demands that 3 is added to 7 (7 is larger or equal to 5) before we do the shift.

The rationale of this algorithm is the following. If the number is 5 or larger, after shift left, we will get 10 or larger, which cannot fit into a BCD digit. Therefore if the number 5 (or larger) we add 3 to it (after shifting is adding 6), which measure we carry forward a 1 to the next BCD digit.

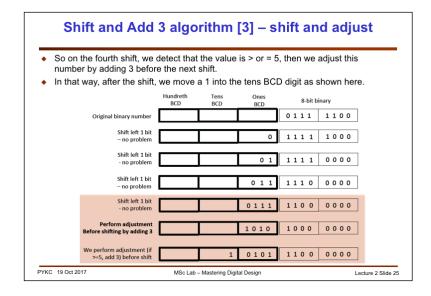

## Shift and Add 3 algorithm [4] - full conversion

- In summary, the basic idea is to shift the binary number left, one bit at a time, into

locations reserved for the BCD results.

- Let us take the example of the binary number 8'h7C. This is being shifted into a 12-bit/3 digital BCD result of 12'd124 as shown below.

|                                     | Hundreth<br>BCD | Tens<br>BCD | Ones<br>BCD | 8-bit binary |         |

|-------------------------------------|-----------------|-------------|-------------|--------------|---------|

| Original binary number              |                 |             |             | 0 1 1 1      | 1 1 0 0 |

| Shift left three times<br>no adjust |                 |             | 0 1 1       | 1110         | 0       |

| Shift left<br>Ones = 7, ≥5          |                 |             | 0 1 1 1     | 1100         |         |

| Add 3                               |                 |             | 1010        | 1 1 0 0      |         |

| Shift left<br>Ones = 5              |                 | 1           | 0 1 0 1     | 1 0 0        |         |

| Add 3                               |                 | 1           | 1000        | 1 0 0        |         |

| Shift left 2 times<br>Tens = 6, ≥5  |                 | 1 1 0       | 0010        | 0            |         |

| Add 3                               |                 | 1 0 0 1     | 0010        | 0            |         |

| Shift left<br>BCD value is correct  | 1               | 0 0 1 0     | 0 1 0 0     |              |         |

To recap: the basic idea is to shift the binary number left, one bit at a time, into locations reserved for the BCD results. Let us take the example of the binary number 8'h7C. This is being shifted into a 12-bit/3 digital BCD result as shown above.

MSc Lab - Mastering Digital Design

Lecture 2 Slide 26

After 8 shift operations, the three BCD digits contain respectively: hundredth digit = 4'b0001, tens digit = 4'b0010 and ones digit = 4'b0100, thus representing the BCD value of 124.

The key idea behind the algorithm can be understood as follow (see the diagram in the slide):

- 1.Each time the number is shifted left, it is multiplied by 2 as it is shifted to the BCD locations;

- 2.The values in the BCD digits are the same as as binary if its value is 9 or lower. However if it is 10 or above it is not correct because for BCD, this should carry over to the next digit. A correction must be made by adding 6 to this digit value.

- 3.The easiest way to do this is to detect if the value in the BCD digit locations are 5 or above BEFORE the shift (i.e. X2). If it is  $\geq$ 5, then add 3 to the value (i.e. adjust by +6 after the shift).

25 26

PYKC 19 Oct 2017

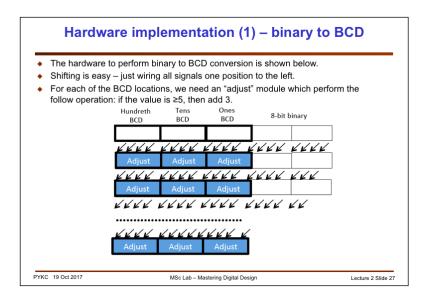

In order to understand how to we may implement this converter in hardware, you have to understand that shifting in hardware is easy. You just need to connect signals with one bit shift to the left. It DOES NOT need any gates, just wires!

Now we also need to do the adjust module, which simply performs the operation:

if

$$(in >= 5)$$

out =  $in + 3$  else out =  $in$

The easiest way to implement such a module is to use a **case statement**. This is set as a tutorial problem in Problem Sheet 1.

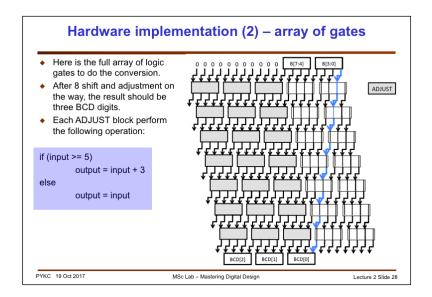

The entire full array is shown here. The shade module is the adjust module (which we call: add3 ge5).

As I said in the last slide, the easiest way to implement (specify) add3\_ge5 is using a case statement.

The BLUE signal path traces what happens to the least significant bit of the original number.

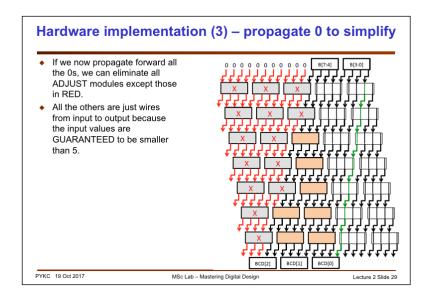

The full array is more complicated than need be. If we propagate the '0's forward in the array of gates, you will find those marked with 'X' will always have its input less than 5. In which, **output = input** in these modules. THIS IS JUST A SET OF FOUR WIRES.

The only remaining add3\_ge5 modules are those shaped in orange.

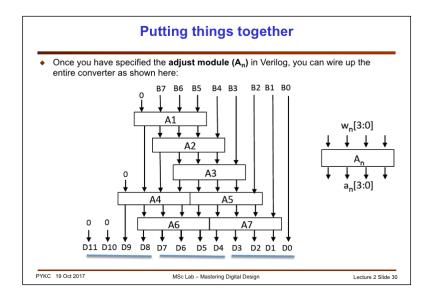

After simplification, here are ALL the remaining <code>add3\_ge5</code> modules for the 8-bit binary to BCD conversion (bin2bcd8). I have labeled the input ports to <code>add3\_ge3 wn[3:0]</code> and the output parts <code>an[3:0]</code> where n is 1 to 7.

#

Assuming that we have designed a module "add3\_ge5" to perform the adjustment as required, the converter can be implemented in Verilog by simply "WIRING UP" the various modules together.

The interconnections are specified in the wire statements.

The next block is instantiating 7 add3\_ge5 modules.

The next block of code is to wire the modules together.

Finally the last statements are to connect up the signals from the modules to the output ports.